I recall burning three or four weeks of a sabbatical getting Saccade.com on the air with Wordpress. So much tweaking…

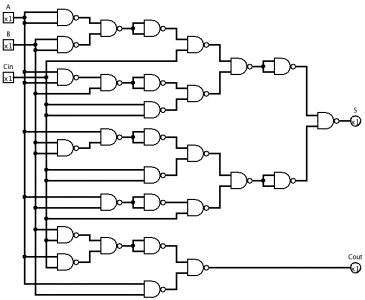

Designing a full adder with logisim

An anonymous commenter suggested that I look at logisim, a circuit simulator written in Java. It has many nice features. For instance, you can specify a combinatorial circuit either as a truth table or as equations, and it will convert to the other representation (in minimized forms) and will also build a circuit to implement those equations. You can tell it to use only 2 input gates, or even to use only NAND gates, and it will layout a little circuit to implement it.

For instance, I entered the truth table for a full adder, and told it just to use 2 input NAND gates. The resulting (29 gates? I didn’t count carefully) 1 bit full adder emerged as a circuit:

Pretty neat. I am not sure that logisim is quite good enough to design an actual, physical CPU (it doesn’t model propagation delays, as far as I can tell) but it’s a very good tool to exercise your nascent digital design skills. Check it out.

Comments

Comment from Mark VandeWettering

Time 7/12/2011 at 9:18 am

I have that book on my shelf. It’s got a very interesting CPU design, in that it’s almost trivially simple CPU, which is bootstrapped into a relatively powerful CPU. I am beginning to believe that even though using logisim to design a CPU may not result in the final product, that it will give me valuable practice and learning, so I’ll probably start there.

Comment from Chris Johnson

Time 7/12/2011 at 10:50 am

Logisim does simulate propagation delays, up to a fashion. The documentation has more details: http://ozark.hendrix.edu/~burch/logisim/docs/2.7/en/html/guide/prop/index.html You may be right about its unsuitability for real probjects: of the many logisim cpus on the web, I have yet to find one that has also been build in hardware.

It seems to me that an ideal circuit would not rely on ‘race conditions’ and so be independent of propagation delays. Is it impractical to design a circuit like this?

Comment from Mark VandeWettering

Time 7/12/2011 at 3:48 pm

Hey Chris, thanks for pointing out the documentation (which I admittedly hadn’t read with any thoroughness).

Since I have no real practical experience, I probably shouldn’t comment on whether it is impractical to design a CPU which operates independent of timing delays, but my limited experience tells me that it simply isn’t done that way. You could (to me it seems) make such a processor work if you ran the clock at an arbitrarily slow, so that any propagation delays have ample time to stabilize, but that doesn’t really achieve a practical design. Even then, odd things can happen.

Take for instance a circuit which implements A & (NOT A). This should be always false. But let’s build a circuit that implements that. We basically feed an AND gate directly with A, and also with A running through an inverter. Let’s begin with A in the 0 state. That is presented unchanged to one input of the AND gate, and simultaneously to the input to the inverter. 10ns or so later (for a 74LS04 hex inverter) the output to the inverter (and the other input to the AND gate) goes high. 0 & 1 = 0, and the AND gate continues to output a false. But now, let’s let A go high. It’s presented to the input to the AND gate, and the output of the inverter is still high, and will stay that way for another 10ns. That means the AND gate outputs a 10ns positive pulse.

Whether that screws anything up is of course dependent on how the circuit is used, but judging by Dawid’s experience in building his own physical CPU, it seems rather likely that problems can creep in.

This isn’t to say that logisim isn’t an excellent learning tool: in fact, I think I am going to use it for my first project, before embarking on a more time consuming path like either writing my own simulator or building hardware. It seems obvious to me that getting a CPU implemented in a system like logisim (even if it isn’t sufficient to design actual hardware) will provide valuable insight into the design process.

Comment from Francisco

Time 7/12/2011 at 8:51 am

For learning fundamental digital design, have a look at http://www1.idc.ac.il/tecs/ if you haven’t already. Again, simulating propagation delays is not the point so I doubt it makes an ideal design tool.